1. Organisasi Processor

Hal-hal yang perlu dilakukan CPU adalah :

- Fetch Instruction = mengambil instruksi

- Interpret Instruction = Menterjemahkan instruksi

- Fetch Data = mengambil data instruksi

- Process Data = mengolah data

- Write data = menulis data

Agar dapat melakukan hal-hal diatas maka CPU perlu menyimpan data untuk sementara waktu

- Agar dapat melakukan hal-hal diatas maka CPU perlu menyimpan data untuk sementara waktu

- CPU harus dapat mengingat lokasi instruksi terakhir sehingga CPU akan dapat mengambil instruksi berikutnya.

- CPU perlu menyimpan instruksi dan data untuk sementara waktu pada saat instruksi sedang di eksekusi. sementara waktu pada saat instruksi sedang di eksekusi.

- Dengan kata lain CPU memerlukan memori internal berukuran kecil.

2. Organisasi Register

Register dalam CPU memiliki dua fungsi :

- User-visible Register

- Control dan Status Register

A. User-Visible Register

Adalah register yang dapat direferensikan dengan menggunakan bahasa mesin yang dengan menggunakan bahasa mesin yang dieksekusi CPU

Terdiri dari :

- General Purpose =dapat berisi operand sembarang op-code

- Data = hanya dapat dipakai untuk menampung data

- Alamat = dapat di gunakan untuk mode pengalamatan tertentu

- Kode-kode kondisi (flag) = bit-bit yang di setel perangkat keras CPU sebagai hasil operasi

B. Control dan Status Register

Adalah register-register yang digunakan oleh unit kontrol untuk mengontrol operasi CPU dan oleh program sistem operasi untuk mengontrol eksekusi program CPU dan oleh program sistem operasi

untuk mengontrol eksekusi program

Adalah register-register yang digunakan oleh unit kontrol untuk mengontrol operasi CPU dan oleh program sistem operasi untuk mengontrol eksekusi program CPU dan oleh program sistem operasi

untuk mengontrol eksekusi program

Terdapat empat buah register yang penting

- Program Counter (PC) berisi alamat instruksi yang akan berisi alamat instruksi yang akan di ambil.

- Instructions Register (IR) berisi instruksi yang berisi instruksi yang terakhir diambil

- Memory Address Register (MAR) Berisi alamat sebuah lokasi di dalam memori

- Memory Buffer Register (MBR) Berisi sebuah word data yang akan dituliskan kedalam memori atau word yang terakhir di baca

Program Status Word (PSW)

- Semua rancangan CPU mencakup sebuah register atau sekumpulan register sering kali disebut Program Status Word (PSW) yang berisi informasi status.

- Biasanya PSW berisi kode kondisi dan informasi status lainnya

Common field atau flag meliputi hal-hal berikut ini:

- Sign = berisi bit tanda hasil operasi aritmetika terakhir

- Zero = disetel bila hasil sama dengan nol terakhir

- Carry = disetel apabila operasi yang dihasilkan didalam carry (penambahan) kedalam bit yang lebih tinggi atau borrow (pengurangan) dari bit yang lebih tinggi

- Equal = disetel apabila hasil pembandingan logikanya sama

- Overflow = digunakan untuk mengindikasikan overflow aritmetika

- Interrupt enable / disable = di gunakan untuk mengizinkan atau mencegah interrupt

- Supervisor = mengindikasikan apakah CPU sedang mengeksekusi dalam mode supervisor atau dalam mode user.

3. Siklus Instruksi

A. Proses Tak Langsung

A. Proses Tak Langsung

- Eksekusi sebuah instruksi melibatkan sebuah operand atau lebih di dalam memori, yang masing-masing operand memerlukan akses memori

- Apabila digunakan pengalamatan tak langsung, maka diperlukan akses memori tambahan

- Kita dapat menganggap pengambilan alamat-alamat tak langsung sebagai sebuah sub instruksi atau lebih.

- Kegiatan utamanya terdiri dari aktifitasaktifitas pengambilan instruksi dan pengeksekusian instruksi.

- Operand yang dibutuhkan diambil dengan menggunakan pengalamatan tak langsung

- Setelah eksekusi dilakukan, interrupt dapat diproses sebelum mengambil instruksi berikutnya

- Pada saat pengambilan instruksi di baca dari memori

- Dalam CPU, PC berisi alamat berikutnya yang akan diambil

- Alamat ini di pindahkan ke MAR dan ditaruh di bus alamat

- Unit control meminta pembacaan memori dan hasilnya disimpan di bus data dan disalin ke MBR dan kemudian di pindahkan ke IR

- Sementara itu PC naik nilainya 1, sebagai persiapan untuk pengambilan selanjutnya.

- Bila siklus pengambilan telah selesai, Unit kontrol memeriksa isi IR untuk menentukan apakah IR berisi operand specifier yang menggunakan

- pengalamatan tak langsung

- Apabila berisi operand maka dilakukan siklus tak langsung

4. Pipelining Instruksi

- Efesiensi sebuah sistem komputer dinilai berdasarkan kecepatan perangkat keras dan fasilitas-fasilitas perangkat lunak.

- Penilaian ini disebut dengan troughput =jumlah pemrosesan yang dapat dikerjakan dalam suatu interval waktu tertentu.

- Salah satu teknik yang mendorong peningkatan suatu sistem troughput yang cukup hebat disebut sebagai pemrosesan PIPELINE

- Pemrosesan Pipeline dalam suatu komputer diperoleh dengan membagi suatu fungsi yang akan dijalankan menjadi beberapa sub fungsi

- yang lebih kecil dan merancang perangkat keras yang terpisah (STAGE), untuk setiap sub fungsi.

- Stage-stage itu kemudian bersama-sama membentuk pipeline tunggal untuk menjalankan fungsi asli

- Pada semua baris perakitan industri, efesiensi suatu pipeline dapat berkurang jauh akibat suatu bottleneck.

- Bottleneck terjadi sewaktu pemrosesan pada suatu stage, menghabiskan waktu lebih lama dari stage yang lain

- Karena itu idealnya kita menginginkan pada semua stage menghabiskan waktu yang sama.

- Untuk menyamakan waktu yang diperlukan pada setiap stage maka stage- stage tersebut harus di sinkronisasi.

- Dapat dilakukan dengan menyisipkan kunci-kunci sederhana antara stage-stage tersebut.

- Suatu fungsi pipeline hampir selalu lebih baik dari pada fungsi non-pipeline

- Namun pada kenyataannya, harga pipeline tersebut sangat mempengaruhi kapan dan apakah fungsi-fungsi yang di pipeline-kan lebih baik atau tidak.

- Tambahan kunci (latch) perangat keras yang dibutuhkan.

- Kendali yang diperlukan untuk penjadwalan input tersebut.

- Waktu yang dihabiskan oleh data dalam latch untuk menyesuaikan diri dengan suatu penangguhan clock yang seragam

- Jumlah rata-rata input yang tersedia

Klasifikasi Pipeline:

A. Klasifikasi berdasarkan Fungsi

A. Klasifikasi berdasarkan Fungsi

- Pipelining Aritmatika = Proses segmentasi fungsi dari ALU dari sistem yang muncul dalam kategori ini.

- Proses fetch pada instruksi tidak akan dimulai sampai eksekusi tidak akan dimulai sampai eksekusi instruksi sebelumnya selesai.

- Untuk mem-pipelinekan fungsi ini, instruksiinstruksi yang berdampingan di fetch dari memori ketika instruksi yang sebelumnya di decode dan di jalankan.

- Proses pipelining instruksi disebut instructions

- Sewaktu stage dari suatu stage merupakan merupakan prosessor aktual dan latch-latch saling berbagi memori antara prosessor-prossor tersebut maka pipeline itu disebut sebagai pipeline prossor.

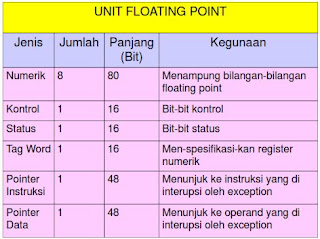

5. Register-register Processor Pentium

Gambar Unit Integer

0 komentar :

Posting Komentar